Intel đang tiến gần đến việc hoàn thiện Z-Angle Memory (ZAM), một hướng bộ nhớ mới nhằm tạo ra lựa chọn thay thế khả thi để cạnh tranh với bộ nhớ băng thông cao (HBM) trong làn sóng AI.

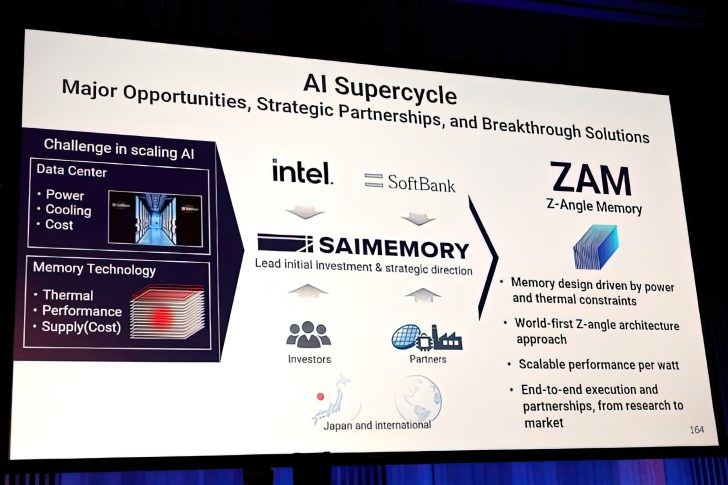

ZAM là chuẩn bộ nhớ đang được Intel phát triển cùng SoftBank, với mục tiêu tạo ra bộ nhớ có mật độ cao nhưng tiêu thụ điện thấp hơn HBM. Theo các thông tin mới được chia sẻ, ZAM được kỳ vọng đạt băng thông gấp 2 lần HBM4, thậm chí tiệm cận cả HBM4E - chuẩn thế hệ kế tiếp được cho là phải sang năm mới xuất hiện. Tuy vậy, ZAM vẫn nhắm mốc 2028-2030 mới tiến tới giai đoạn sản xuất, nên đây chưa phải công nghệ sẽ sớm có mặt trên thị trường.

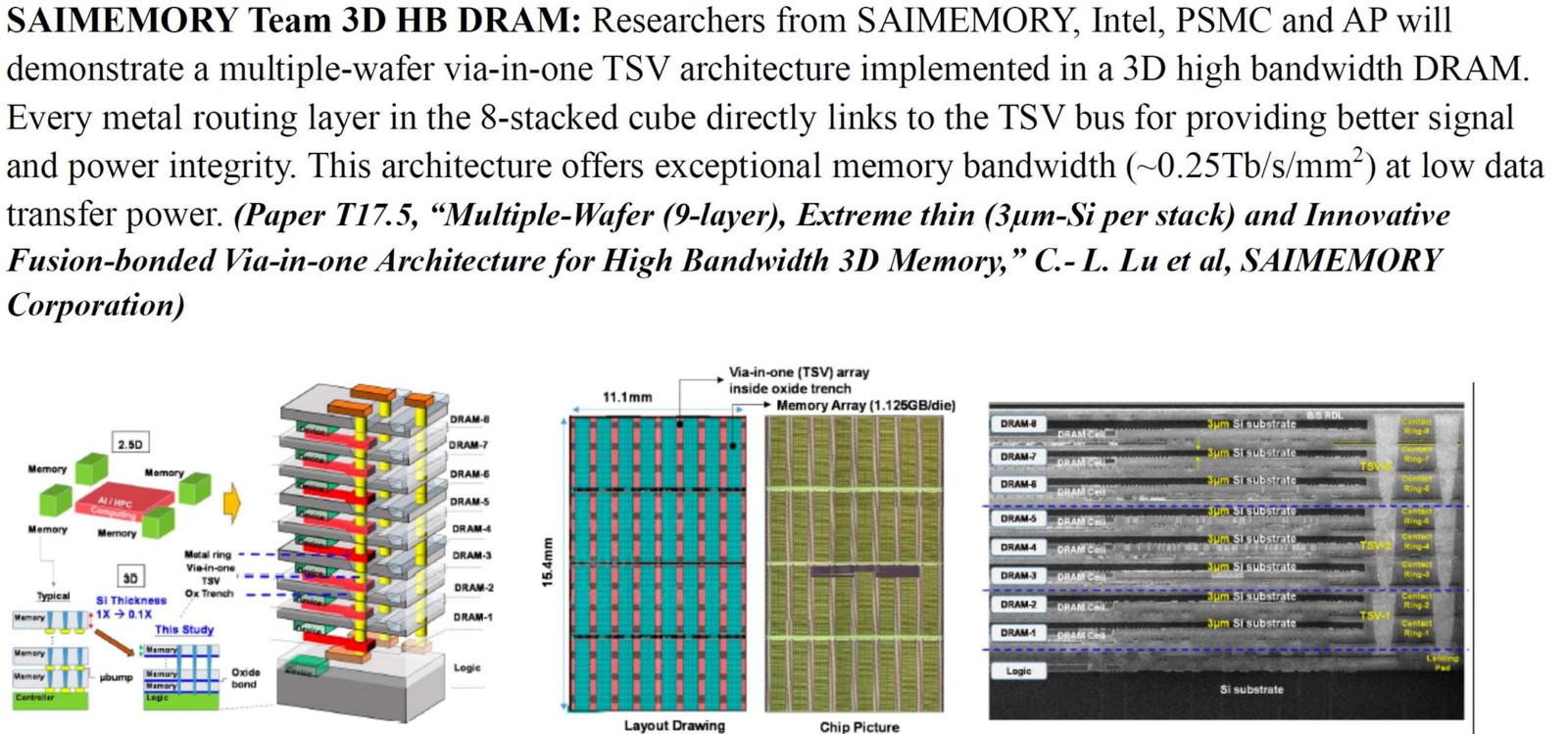

Tại hội thảo VLSI năm 2026, Intel và công ty con của SoftBank là SAIMEMORY dự kiến công bố thêm chi tiết, đồng thời đã hé lộ một số đặc tính của ZAM. Ở phần thiết kế, ZAM được trình diễn với cấu trúc xếp chồng 9 tầng. Mỗi cụm xếp chồng gồm 8 tầng DRAM, giữa mỗi tầng có một lớp nền silicon dày 3 micron. Phần nền chính tích hợp một bộ điều khiển logic để điều phối hoạt động của toàn bộ cụm bộ nhớ.

Về kết nối, ZAM có 3 lớp lỗ xuyên silicon (TSV), mỗi lớp chứa khoảng 13,7 nghìn đường liên kết xuyên qua lớp nền, dùng kỹ thuật liên kết lai. Dung lượng được nêu là 1,125 GB cho mỗi tầng, tương ứng khoảng 10 GB cho mỗi cụm xếp chồng, và đạt 30 GB cho toàn bộ gói. Kích thước cụm ZAM khoảng 171 mm2 (15,4 x 11,1 mm). Intel cũng đưa ra mật độ băng thông khoảng 0,25 Tb/s trên mỗi mm2, tương đương 5,3 TB/s cho mỗi cụm xếp chồng.

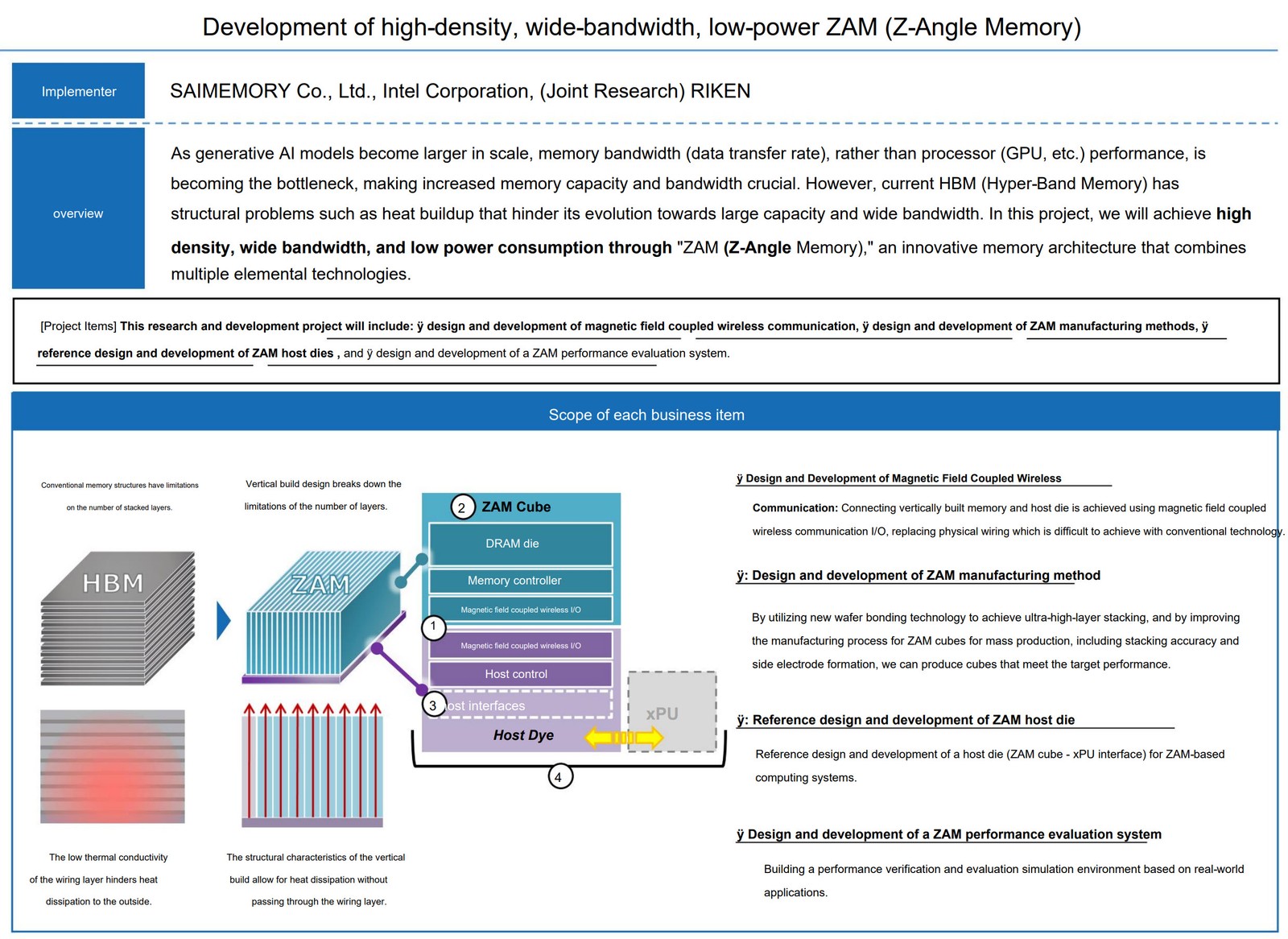

Hiện nay, HBM là lựa chọn phổ biến cho các bộ tăng tốc AI và GPU hiệu năng cao, nhưng khi mở rộng quy mô thường kéo theo thách thức về nhiệt và điện năng. ZAM được giới thiệu để giải quyết 3 điểm chính: mật độ cao, băng thông rộng và tiêu thụ điện thấp hơn. Nhờ cấu trúc dựng theo phương thẳng đứng, ZAM được kỳ vọng tản nhiệt tốt hơn mà không phải đưa nhiệt đi qua lớp dây dẫn như một số cấu trúc xếp chồng khác.

Intel mô tả ZAM có thể đạt mật độ băng thông cao hơn, tối ưu điện năng cho truyền dữ liệu, tản nhiệt tốt hơn, hỗ trợ xếp chồng từ 9 tầng trở lên nhờ lớp silicon cực mỏng 3 micron và cấu trúc TSV tích hợp. Ngoài ra, thiết kế còn nhắc tới cách vào ra dữ liệu không dây ghép bằng từ trường, cùng kỹ thuật liên kết tiên tiến để tăng khả năng mở rộng. Về dài hạn, mục tiêu của ZAM là đi tới thiết kế bộ nhớ 3D dày đặc thông qua đóng gói 3.5D, đặt các lớp theo cả chiều dọc lẫn chiều ngang trên cùng một nền, bao gồm cụm bộ nhớ băng thông cao dung lượng lớn, đường cấp nguồn và tiếp địa, quang tử silicon và các kênh vào ra truyền thống.

Max