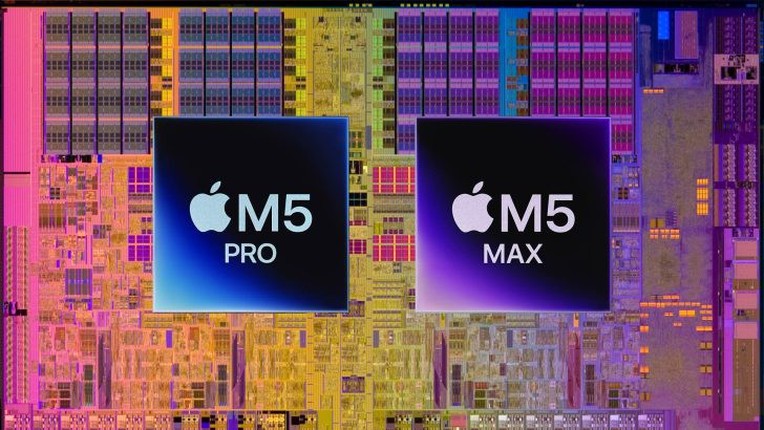

Apple đã áp dụng "Fusion Architecture" lần đầu tiên trên M5 Pro và M5 Max, đánh dấu sự thay đổi đáng kể so với kiến trúc đơn chip (monolithic) từng được dùng trên các thế hệ Apple Silicon trước đó. Thay vì thiết kế 2.5D thông thường - nơi các khối chức năng nằm trên cùng một mặt phẳng của die - M5 Pro và M5 Max sử dụng các dies xếp chồng theo chiều dọc, tương tự nhưng không đồng nhất với đóng gói 3D.

Thông tin này đến từ cuộc phỏng vấn của Anand Shimpi với ấn phẩm công nghệ Đức Heise online. Shimpi, cựu trưởng biên tập Anandtech, hiện làm việc trong bộ phận Hardware Technologies của Apple. Ông cho biết kinh nghiệm tích lũy từ kiến trúc UltraFusion trên M2 Ultra và M3 Ultra đã được Apple vận dụng để phát triển Fusion Architecture mới cho M5 Pro và M5 Max.

"Về cơ bản đây là phiên bản mới hơn của một khái niệm tương tự. Với các chip Ultra trước đây, chúng tôi kết hợp hai SoC giống hệt nhau để tạo ra một SoC lớn hơn. Còn giờ, chúng tôi thực sự đã chia một số chức năng trên hai dies khác nhau. Chúng không phải là bản phản chiếu của nhau; chúng tôi đã tích hợp các IP blocks riêng biệt cho từng die", Shimpi giải thích.

Trong thiết kế xếp chồng, các khối CPU, GPU và các thành phần khác được đặt chồng lên nhau theo dạng sandwich, tạo ra giao diện băng thông cao, độ trễ thấp và tiết kiệm điện năng giữa các thành phần. Đánh đổi thường thấy của thiết kế này là nhiệt độ vận hành cao hơn do nhiệt từ các lớp tích lũy lại. Tuy nhiên, trong một bài kiểm tra stress đa nhân trước đó, M5 Max ghi nhận nhiệt độ thấp hơn M4 Max, cho thấy Apple đã kiểm soát tốt vấn đề tản nhiệt dù áp dụng thiết kế xếp chồng.

Cần lưu ý rằng có sự không thống nhất về vai trò thực tế của Shimpi tại Apple. Trong khi Heise online giới thiệu ông là nhân viên kiến trúc nền tảng (platform architecture), tài khoản X @IanCutress - Ian Cutress, cựu chuyên gia phân tích chip tại Anandtech - cho biết Shimpi thực tế thuộc bộ phận phân tích cạnh tranh và tối ưu hóa (competitive analysis and optimization). Sự khác biệt này ảnh hưởng đến độ tin cậy của thông tin về thiết kế dies xếp chồng. Phải chờ thêm xác nhận chính thức hoặc phân tích die shot thực tế mới có thể kết luận chắc chắn.

Max